SONY索尼開發出新款Back-Illuminated 背照式CMOS影像感測器

可通過 Pixel-Parallel 畫素並行A / D轉換器實現全局快門(Global Shutter)功能

(東京,日本)——索尼公司宣佈開發出配備全局快門功能※1,擁有146萬畫素的背照式CMOS影像感測器。新開發的畫素並行模數轉換器能將所有同時曝光的畫素類比信號立即轉換為並行的數位信號。索尼於2018年2月11日在美國三藩市舉行的國際固態電路會議(ISSCC)上展示了這項新技術。

目前市面上的CMOS影像感測器是採用傳統的縱列A/D轉換方法※2逐行讀取由畫素經光電轉換產生的類比信號,這種方式容易產生讀取時移,從而導致影像失真(焦平面失真)。

而這款全新的索尼感測器配有最新研發的低電流緊湊型A/D轉換器,它們位於每個畫素下方。這些A/D轉換器可立即將所有來自同時曝光的畫素類比信號平行轉換為數位信號,並將其暫時存儲在數位記憶體中。這種結構能減少讀取時移導致的焦平面失真,因而具備了全局快門功能※1,這是業界首款※3用於高靈敏度背照式CMOS感測器的百萬畫素級並行A/D轉換器。

與傳統的縱列A/D轉換方法※2相比,新款感測器所用到的A/D轉換器數量增加至約1000倍,這意味著對電流的需求激增了。索尼則通過開發一款緊湊型14位A/D轉換器解決了這個問題,該轉換器在低電流環境下擁有業界最佳性能※4。

新款感測器的A/D轉換器和數位記憶體空間都採用堆疊結構,這些元件集成在底部晶片中。頂部晶片上每個畫素之間的連接使用Cu-Cu(銅 -

銅)連接※5,索尼於2016年1月實現批量生產,這也是該技術首次實現批量生產。

另外,該感測器採用了新開發的資料傳輸機制,能夠在A/D轉換過程中實現高速且大規模地並行資料讀取。

※1:此項功能可有效減少因逐行讀取畫素信號而引起的影像失真(焦平面失真)。

※2:此方法為並行配置中的每個垂直行畫素提供A/D轉換器。

※3:截至2018年2月13日。

※4:截至2018年2月13日。FoM(靈敏值):0.24e-・nJ/step。(功耗×雜訊)/{畫素量×格速×ADC解析度)}。

※5:該技術在累加背照式CMOS影像感測器部分(頂部晶片)和邏輯電路(底部晶片)時,通過連接的Cu(銅)焊盤持續供電。與矽通孔(TSV)佈線相比,該方法通過在畫素區周圍穿透電極來實現連接,讓設計更為自由,生產力更強,尺寸更小,性能更高。索尼於2016年12月在三藩市的國際電子設備會議(IEDM)上展示了該項技術。

主要特點

通過以下核心技術,在高靈敏度的背照式CMOS影像感測器中實現全局快門功能※1

低電流、緊湊型的 pixel-parallel 畫素並行A/D轉換器

為了減少能耗,新轉換器採用了可在亞閾值電流下運行的比較器,這款低電流、緊湊型的14位A/D轉換器,實現了業界性能最佳※4。較之傳統的轉換方法※2,它所採用的A/D轉換器增加至約1000倍,卻依然克服了由此帶來的電流需求壓力。

Cu-Cu (copper-copper) connection 銅 - 銅連接※5

為了實現所有畫素並行的A/D轉換,索尼公司開發了一種技術,可以將大約300萬個銅 - 銅連接※5搭在一個感測器上。銅 - 銅連接提供了畫素和邏輯基板之間的電氣連續性,保證了146萬個(同有效畫素)A/D轉換器和數位記憶體的安全空間。

高速資料傳輸建設

索尼開發了一種新的讀取電路,以支援在A/D轉換過程中所需要的大規模並行數位信號傳輸。該轉換過程會用到146萬個A/D轉換器,以高速讀取和寫入所有的畫素信號。

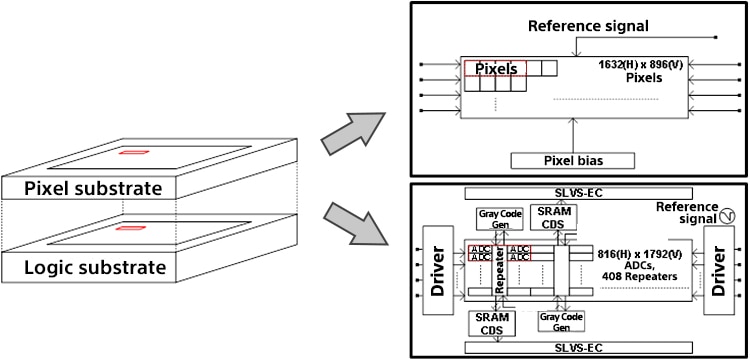

Block diagram 塊圖

晶片照片

(左邊:銅-銅連接橫切面,右上:畫素基板,右下:邏輯基板)

拍攝樣張

((F2.8, 7300lux,曝光時間:0.56毫秒,y1.0)

Key Specifications

| Low power mode | Low noise mode | |

|---|---|---|

| Effective pixels | 1632(H) × 896(V) | |

| Unit cell size | 6.9 [μm] × 6.9 [μm] | |

| Max. frame rate | 660 [fps] | |

| Power consumption | 654 [mW] | 746 [mW] |

| RMS random noise(@ analog gain 0[dB]) | 8.77 [e-rms] | 5.15 [e-rms] |

| Dynamic range | 65.7 [dB] | 70.2 [dB] |

| A/D converter resolving capability | 14 [bit] | |

(本文譯自英文原文)